## **IOWA STATE UNIVERSITY Digital Repository**

Retrospective Theses and Dissertations

Iowa State University Capstones, Theses and Dissertations

1983

# Microprocessor based modular support for an operating system

Ahmed Amin Elamawy Iowa State University

Follow this and additional works at: https://lib.dr.iastate.edu/rtd

Part of the <u>Electrical and Electronics Commons</u>

#### Recommended Citation

Elamawy, Ahmed Amin, "Microprocessor based modular support for an operating system" (1983). Retrospective Theses and Dissertations. 7710.

https://lib.dr.iastate.edu/rtd/7710

This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact digirep@iastate.edu.

#### INFORMATION TO USERS

This reproduction was made from a copy of a document sent to us for microfilming. While the most advanced technology has been used to photograph and reproduce this document, the quality of the reproduction is heavily dependent upon the quality of the material submitted.

The following explanation of techniques is provided to help clarify markings or notations which may appear on this reproduction.

- 1. The sign or "target" for pages apparently lacking from the document photographed is "Missing Page(s)". If it was possible to obtain the missing page(s) or section, they are spliced into the film along with adjacent pages. This may have necessitated cutting through an image and duplicating adjacent pages to assure complete continuity.

- 2. When an image on the film is obliterated with a round black mark, it is an indication of either blurred copy because of movement during exposure, duplicate copy, or copyrighted materials that should not have been filmed. For blurred pages, a good image of the page can be found in the adjacent frame. If copyrighted materials were deleted, a target note will appear listing the pages in the adjacent frame.

- 3. When a map, drawing or chart, etc., is part of the material being photographed, a definite method of "sectioning" the material has been followed. It is customary to begin filming at the upper left hand corner of a large sheet and to continue from left to right in equal sections with small overlaps. If necessary, sectioning is continued again—beginning below the first row and continuing on until complete.

- 4. For illustrations that cannot be satisfactorily reproduced by xerographic means, photographic prints can be purchased at additional cost and inserted into your xerographic copy. These prints are available upon request from the Dissertations Customer Services Department.

- 5. Some pages in any document may have indistinct print. In all cases the best available copy has been filmed.

University

Microfilms

International

300 N. Zeeb Road

Ann Arbor, MI 48106

#### Elamawy, Ahmed Amin

# MICROPROCESSOR BASED MODULAR SUPPORT FOR AN OPERATING SYSTEM

Iowa State University

PH.D. 1983

University

Microfilms

International 300 N. Zeeb Road, Ann Arbor, MI 48106

|  |  | , |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

#### **PLEASE NOTE:**

In all cases this material has been filmed in the best possible way from the available copy. Problems encountered with this document have been identified here with a check mark  $\_\sqrt{}$ .

| 1.  | Glossy photographs or pages                                                      |

|-----|----------------------------------------------------------------------------------|

| 2.  | Colored illustrations, paper or print  Photographs with dark background          |

| 3.  | Photographs with dark background                                                 |

| 4.  | Illustrations are poor copy                                                      |

| 5.  | Pages with black marks, not original copy                                        |

| 6.  | Print shows through as there is text on both sides of page                       |

| 7.  | Indistinct, broken or small print on several pages                               |

| 8.  | Print exceeds margin requirements                                                |

| 9.  | Tightly bound copy with print lost in spine                                      |

| 10. | Computer printout pages with indistinct print                                    |

| 11. | Page(s) lacking when material received, and not available from school or author. |

| 12. | Page(s)seem to be missing in numbering only as text follows.                     |

| 13. | Two pages numbered Text follows.                                                 |

| 14. | Curling and wrinkled pages                                                       |

| 15. | Other                                                                            |

University Microfilms International

|  | , |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

# Microprocessor based modular support for an operating system

by

#### Ahmed Amin Elamawy

A Dissertation Submitted to the

Graduate Faculty in Partial Fulfillment of the

Requirements for the Degree of

DOCTOR OF PHILOSOPHY

Department: Electrical Engineering

Major: Electrical Engineering (Computer

Engineering)

#### Approved:

Signature was redacted for privacy.

In Charge of Major Work

Signature was redacted for privacy.

For the Major Department

Signature was redacted for privacy.

For the Graduate |College

lowa State University Ames, Iowa

1983

## TABLE OF CONTENTS

|                                                                                                | Page           |

|------------------------------------------------------------------------------------------------|----------------|

| CHAPTER I. INTRODUCTION                                                                        | 1              |

| CHAPTER II. LITERATURE REVIEW                                                                  | 4              |

| CHAPTER III. MODULAR MULTI-MICROPROCESSOR BASED SUPPORT FOR AN OPERATING SYSTEM                | 9              |

| Support Modules                                                                                | 10             |

| Reliability                                                                                    | 13             |

| Cost                                                                                           | 14             |

| Other Aspects                                                                                  | 14             |

| CHAPTER IV. SUPPORT MODULE FOR A DEADLOCK AVOIDANCE SCHEME                                     | 16             |

| Introduction                                                                                   | 16             |

| The Need for Hardware Support                                                                  | 20             |

| The Support Module                                                                             | 20             |

| 0(km) module, $k = 1$                                                                          | 22             |

| Operation                                                                                      | 24             |

| 0(km) module, $k > 10(km)$ module, $k < 1$                                                     | 27<br>27       |

| Module Organization                                                                            | 28             |

| CHAPTER V. A MODULE FOR THE EXACT IMPLEMENTATION OF THE LEAST RECENTLY USED REPLACEMENT POLICY | 31             |

| Introduction                                                                                   | 31             |

| Exact LRU Support Module Organization                                                          | 36             |

| Submodule Organization                                                                         | 37             |

| Detailed Submodule Design                                                                      | 41             |

| The microprocessor Arbitration Random Access Memory (RAM)                                      | 42<br>43<br>43 |

|                                                                              | Page           |

|------------------------------------------------------------------------------|----------------|

| Read Only Memory (ROM) The TIMER Decoding and control logic                  | 47<br>49<br>53 |

| Output latches                                                               | 53             |

| Address Stream Generation Module                                             | 54             |

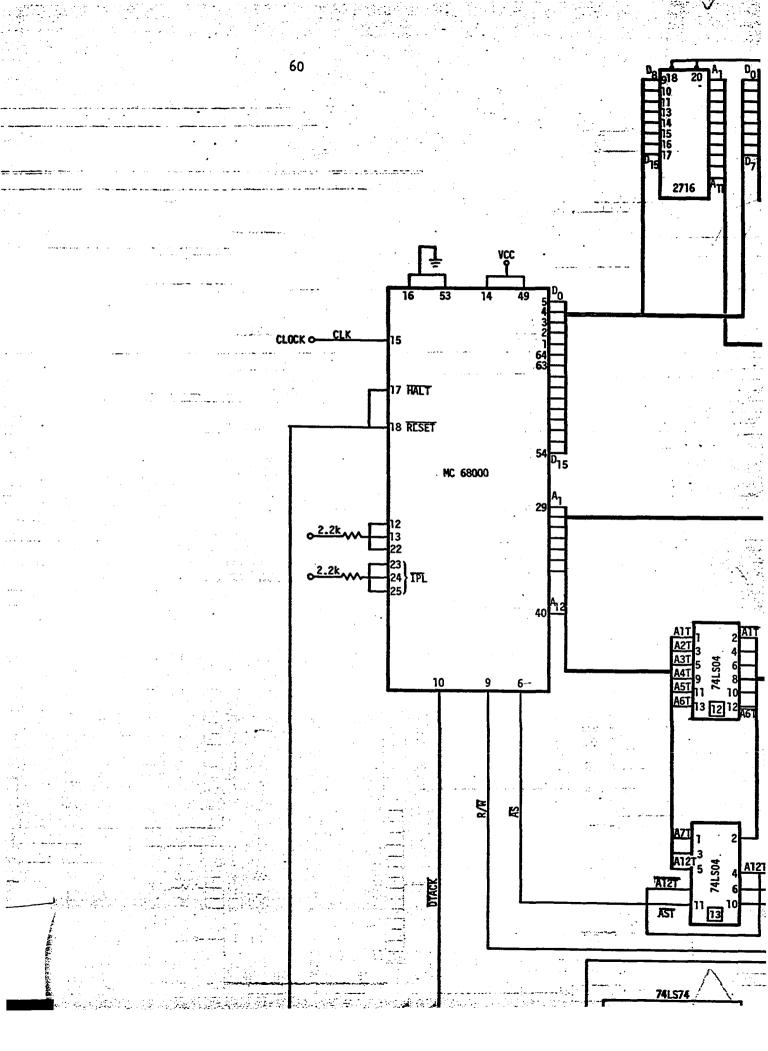

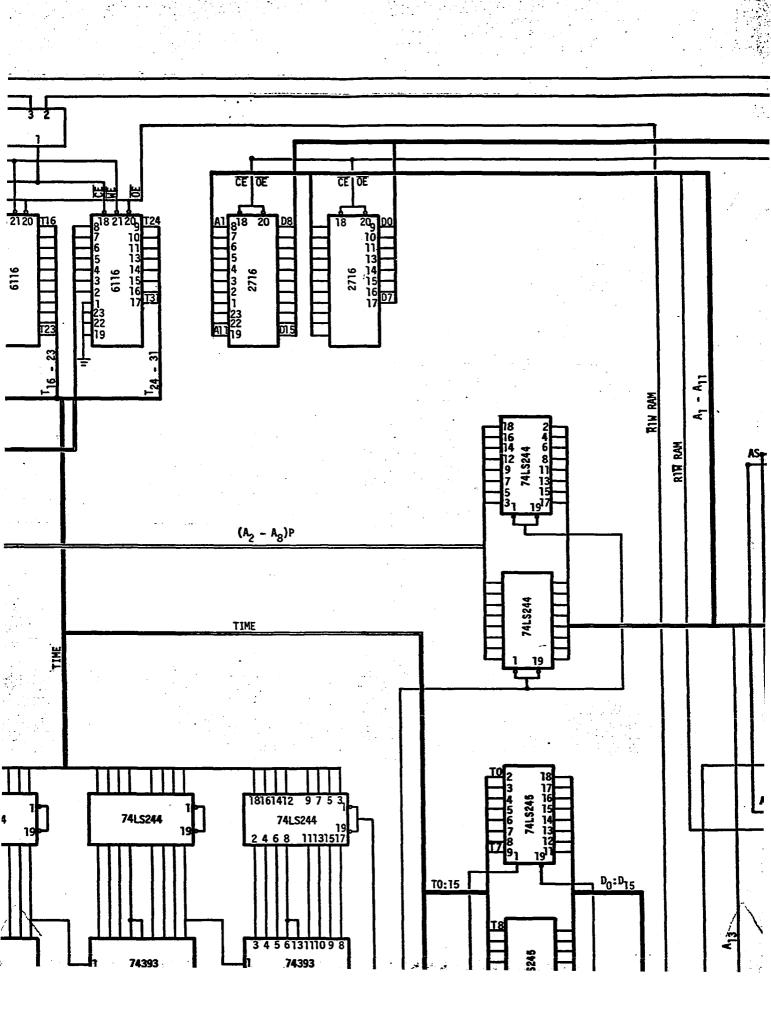

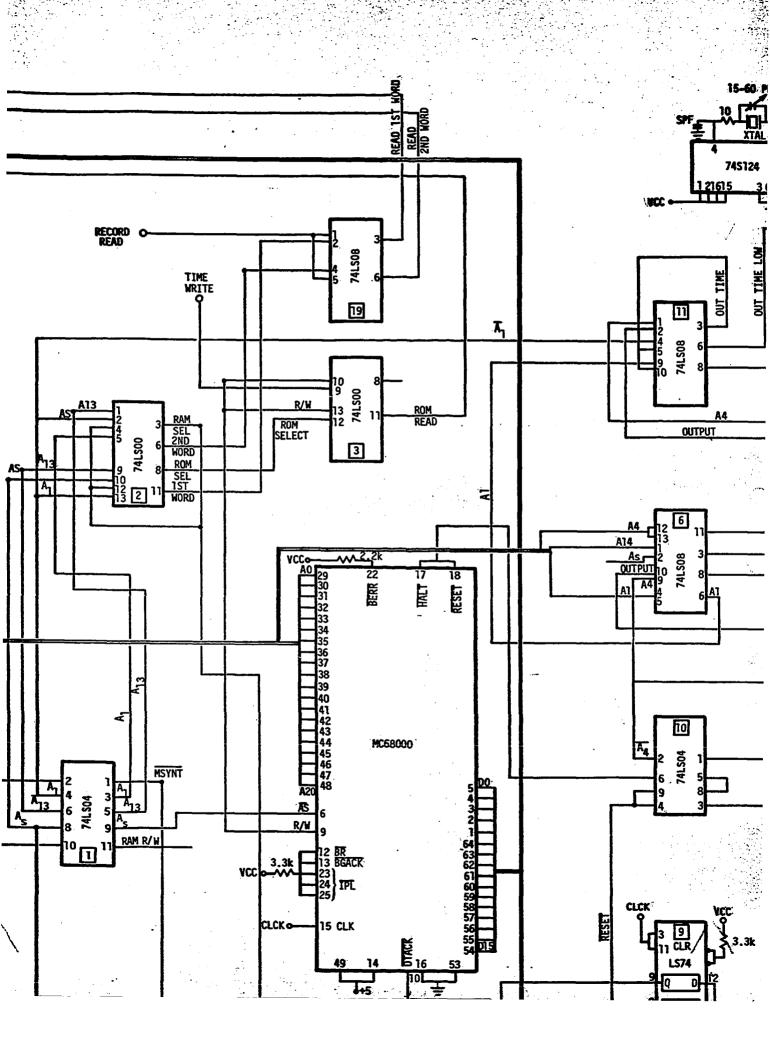

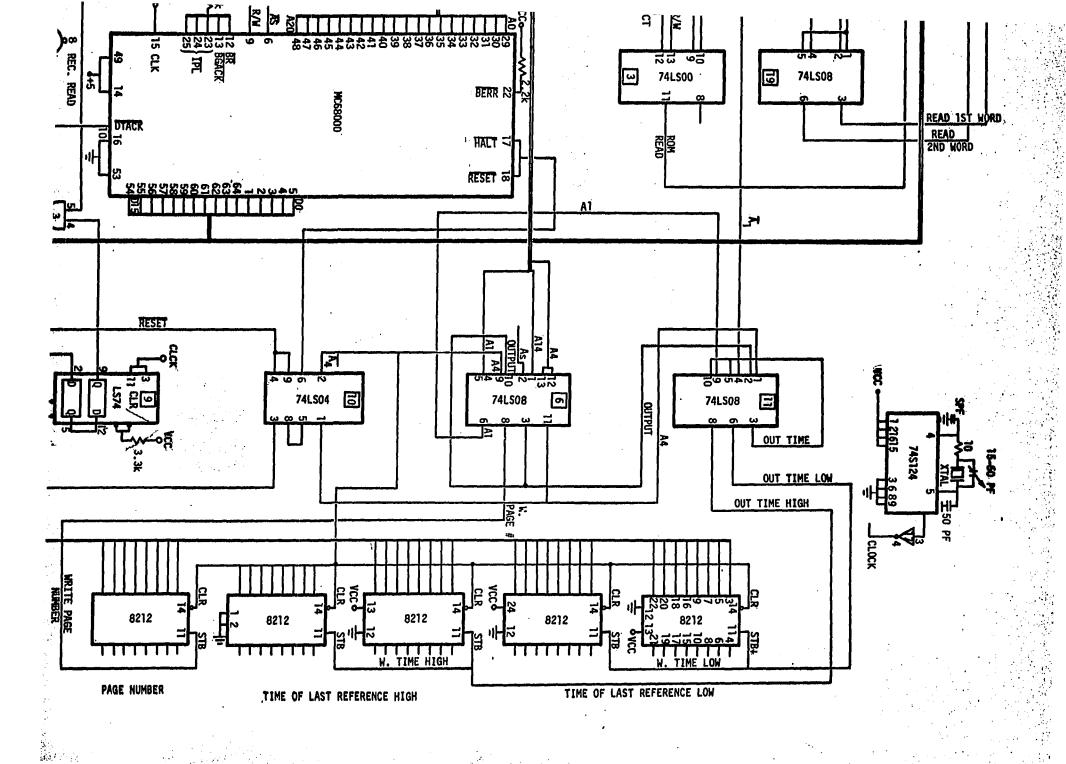

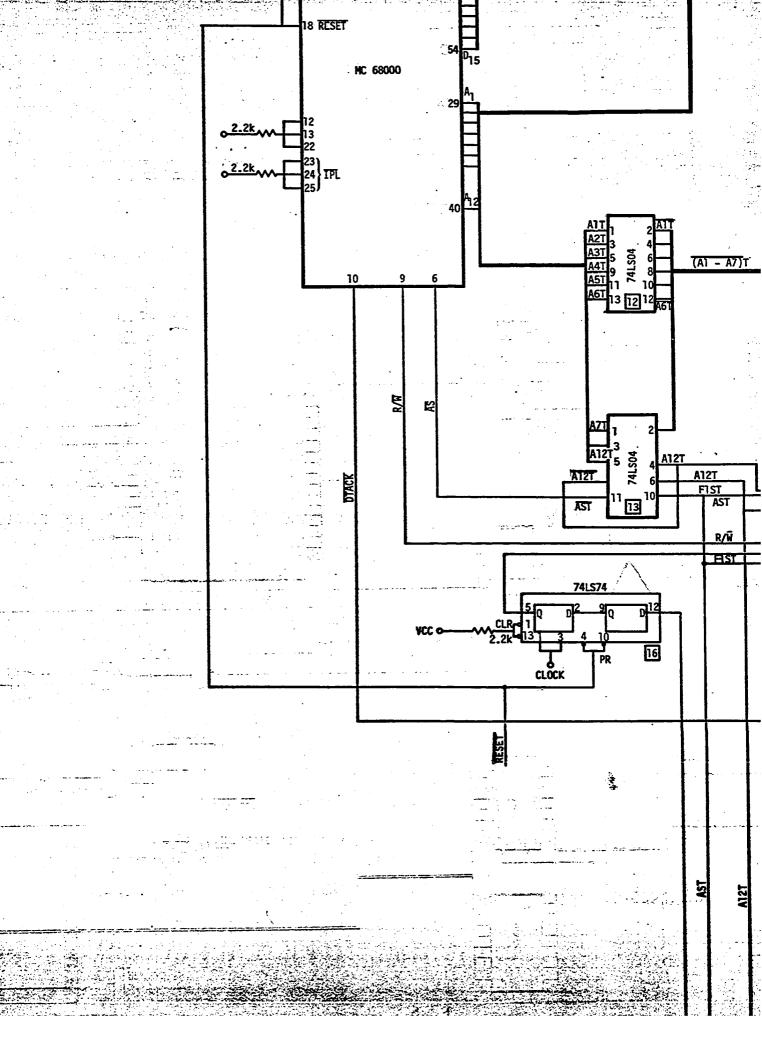

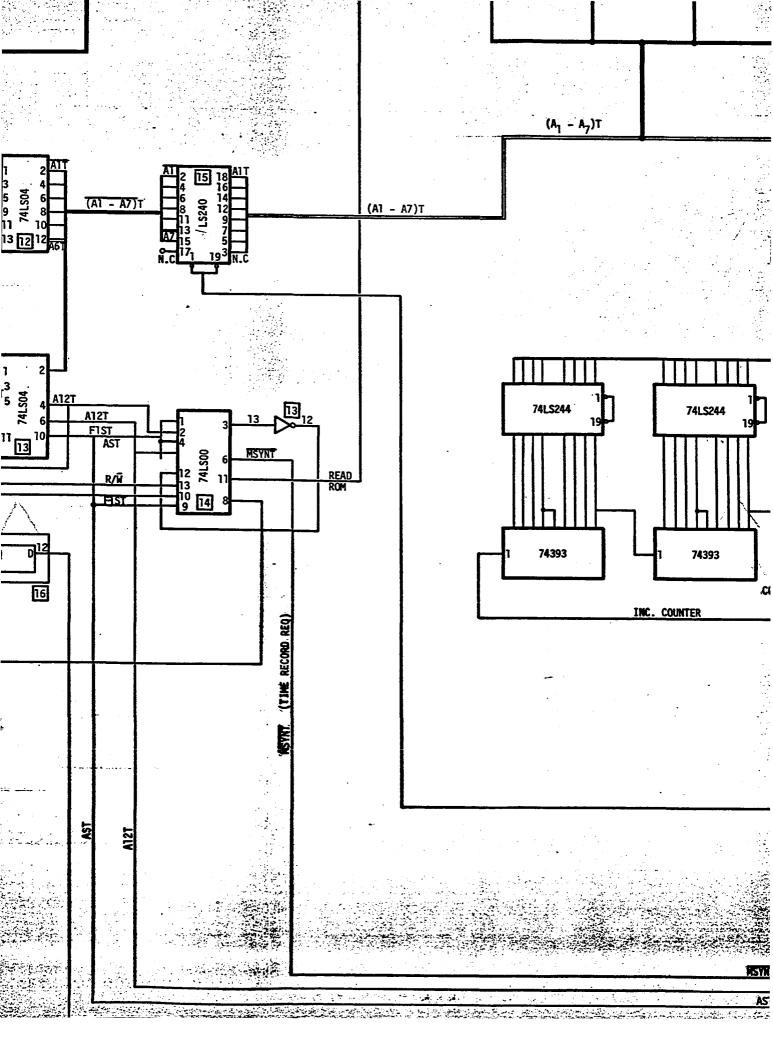

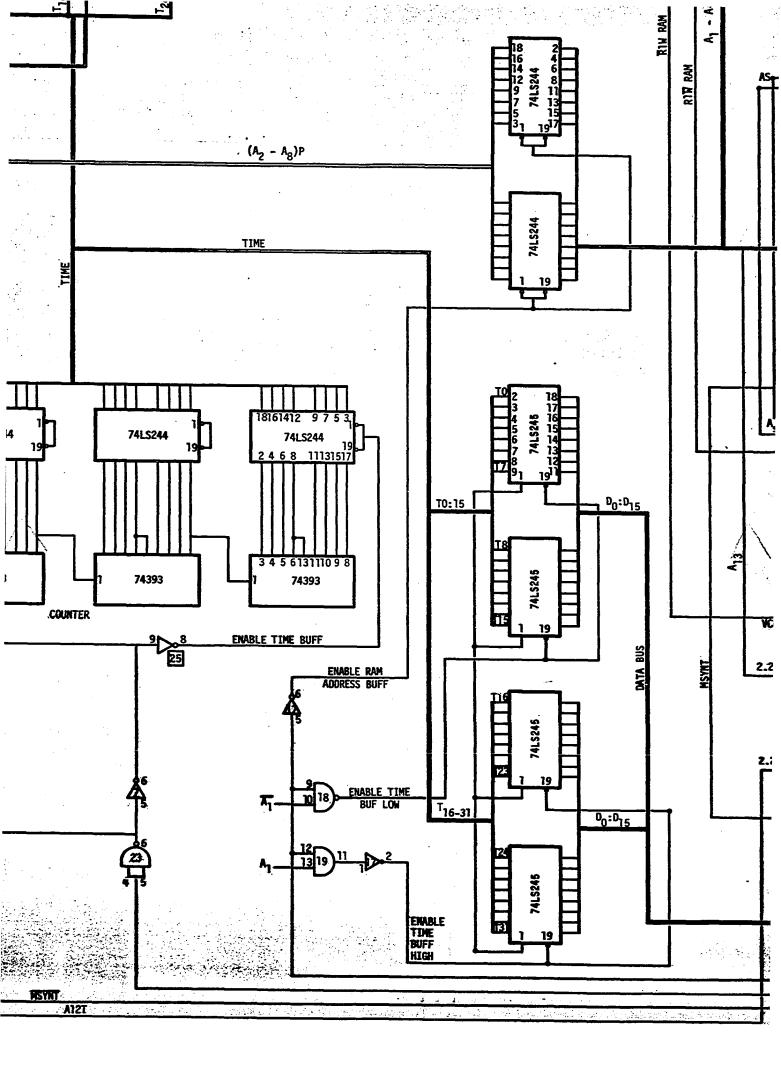

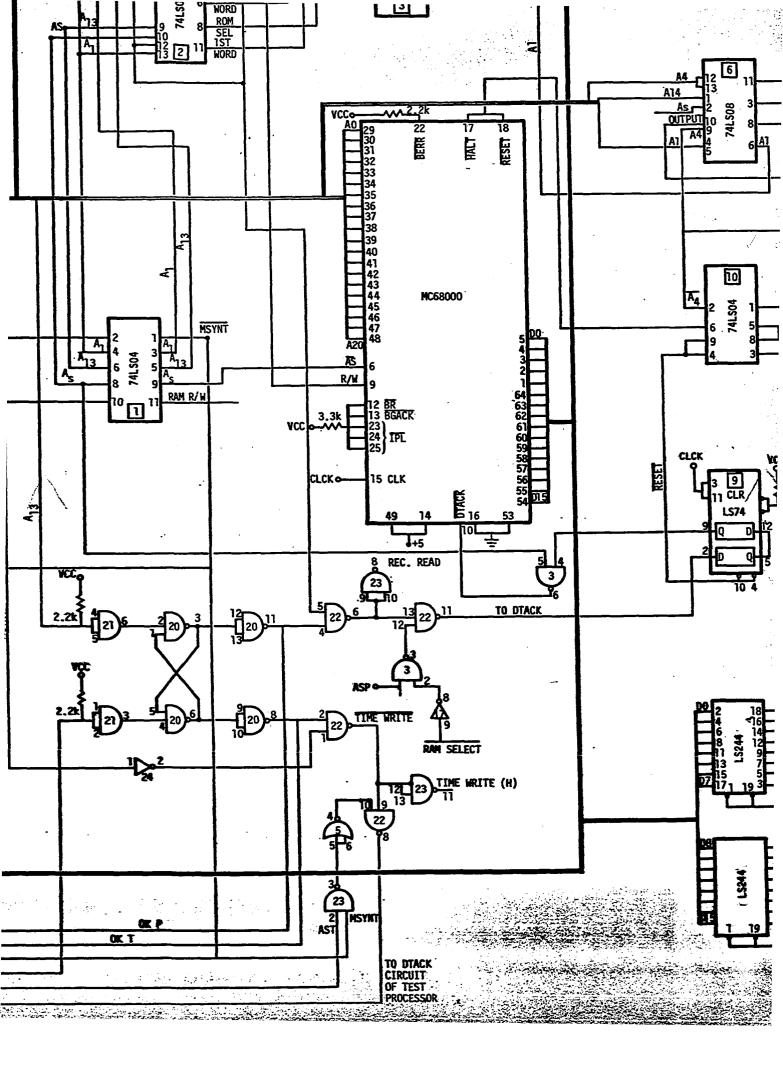

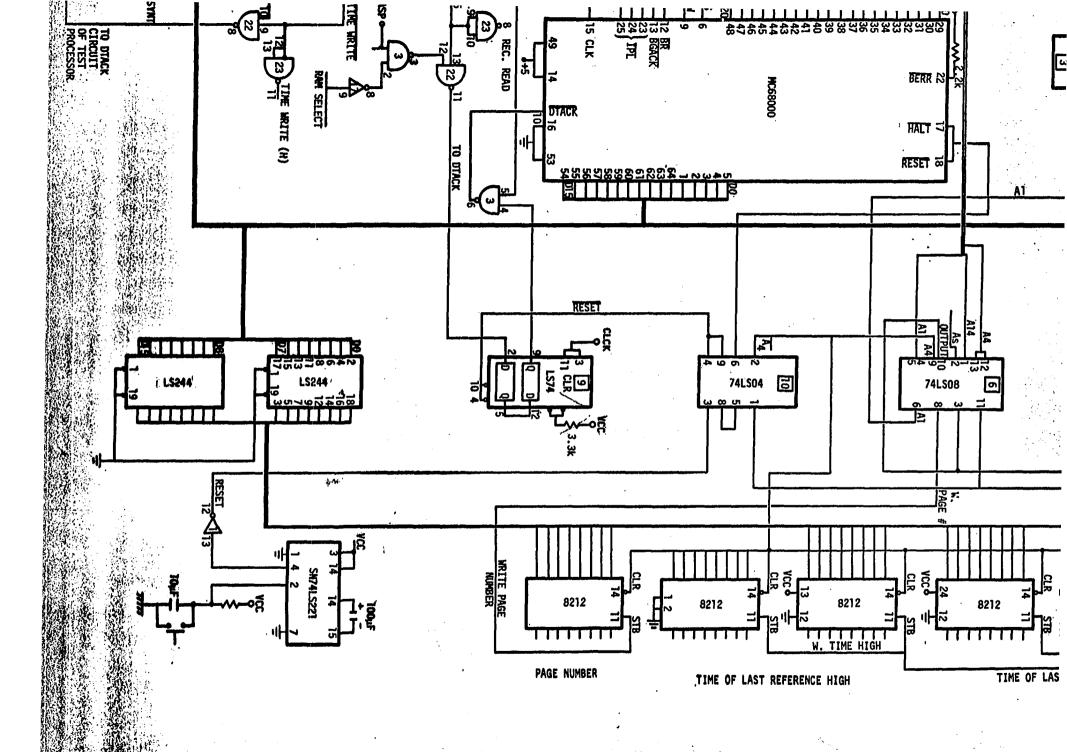

| Detailed Circuit Diagram                                                     | 58             |

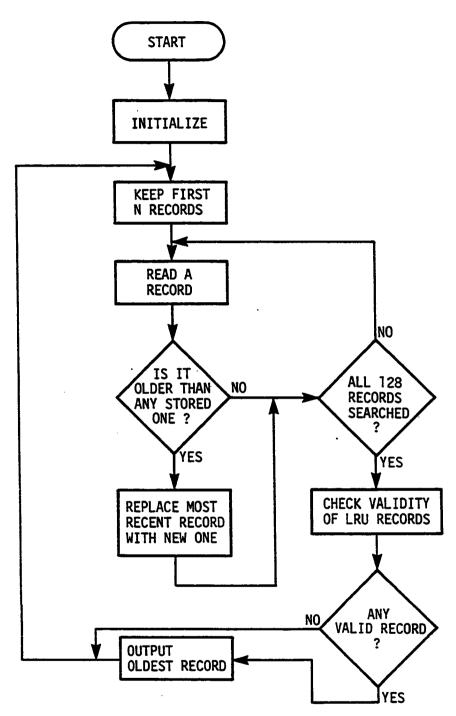

| The LRU Routine                                                              | 63             |

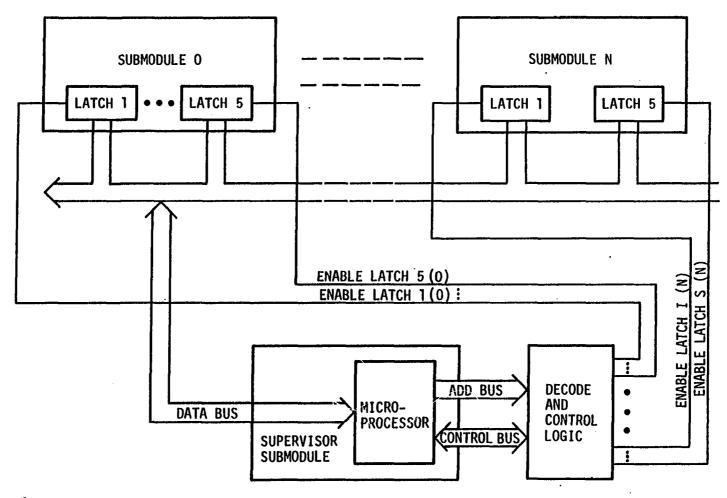

| An LRU Module Overview                                                       | 70             |

| CHAPTER VI. ADDRESS GENERATION ROUTINES, EXPERIMENTAL DATA, AND SOME REMARKS | 75             |

| Address Generation Routines                                                  | 75             |

| Experimental Data                                                            | 82             |

| Remarks and Observations                                                     | 104            |

| Reducing LRU module loading on main system A zero load LRU module            | 105<br>108     |

| CHAPTER VII. CONCLUSION                                                      | 110            |

| BIBLIOGRAPHY                                                                 | 117            |

| ACKNOWLEDGMENTS                                                              | 119            |

| APPENDIX A. ROUTINEI                                                         | 120            |

| APPENDIX B. ROUTINE2                                                         | 121            |

| APPENDIX C. ADDGENI                                                          | 123            |

| APPENDIX D. ADDGEN2                                                          | 126            |

| ADDENDIY E ADDCENS                                                           | 128            |

### LIST OF FIGURES

|        |     |                                                                               | Page      |

|--------|-----|-------------------------------------------------------------------------------|-----------|

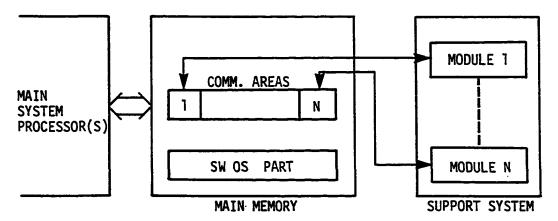

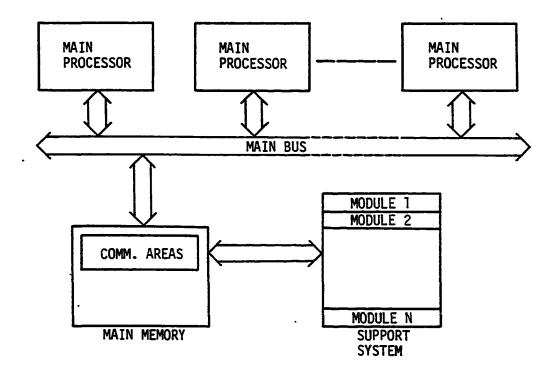

| Figure | 1.  | Communication technique between the support system and the main system        | 11        |

| Figure | 2.  | A homogeneous main system supported by a heterogeneous modular support system | <u>j1</u> |

| Figure | 3.  | Organization of the O(m) module                                               | 23        |

| Figure | 4.  | Hardware substitute for a deadlock avoidance algorithm                        | 29        |

| Figure | 5.  | 0(km), $k < 1$ module organization                                            | 29        |

| Figure | 6.  | Block diagram of the LRU module                                               | 38        |

| Figure | 7.  | LRU submodule organization                                                    | 39        |

| Figure | 8.  | RAM addressing mechanism                                                      | 46        |

| Figure | 9.  | RAM data buffering                                                            | 48        |

| Figure | 10. | The TIMER and its buffering                                                   | 51        |

| Figure | 11. | Time recording timing diagram                                                 | 52        |

| Figure | 12. | Address generation circuit block diagram                                      | 55        |

| Figure | 13. | Address generation routine "ADDGEN4"                                          | 56        |

| Figure | 14. | Detailed diagram of the LRU submodule and the address generation module       | 60        |

| Figure | 15. | A photograph of the built circuits                                            | 62        |

| Figure | 16. | Flow chart of LRU routine                                                     | 64        |

| Figure | 17. | Exact LRU program "ROUTINE3"                                                  | 65        |

| Figure | 18. | Possible connection between output latches and the supervisor submodule       | 72        |

| Figure | 19. | ADDGEN1 sequence (one NOP instruction in each loop)                           | ) 76      |

| Figure | 20. | Address sequence generated by ADDGEN2 (three NOP                              | 78        |

|            |                                                                      | Page |

|------------|----------------------------------------------------------------------|------|

| Figure 21. | Address sequence generated by ADDGEN3 (no NOP instructions are used) | 79   |

| Figure 22. | ADDGEN4 sequence (no NOP instructions included in the loops)         | 80   |

## LIST OF TABLES

|          |                                              | Page |

|----------|----------------------------------------------|------|

| Table 1  | . Key to different experimental data tables  | 83   |

| Table 2  | . ADDGEN1 and ROUTINE1 (one NOP instruction) | 85   |

| Table 3  | . ADDGEN1 and ROUTINE2                       | 86   |

| Table 4  | . ADDGEN1 and ROUTINE3                       | 87   |

| Table 5  | . ADDGEN2 and ROUTINE!                       | 88   |

| Table 6  | . ADDGEN2 and ROUTINE2                       | 89   |

| Table 7  | 7. ADDGEN2 and ROUTINE3                      | 90   |

| Table 8  | 3. ADDGEN3 and ROUTINE!                      | 91   |

| Table 9  | ADDGEN3 and ROUTINE2                         | 92   |

| Table 10 | O. ADDGEN3 and ROUTINE3                      | 93   |

| Table 11 | . ADDGEN4 and ROUTINE1                       | 94   |

| Table 12 | 2. ADDGEN4 and ROUTINE2                      | 95   |

| Table 13 | 3. ADDGEN4 and ROUTINE3                      | 96   |

| Table 1  | 4. Performance of ROUTINE!                   | 99   |

| Table 1  | 5. Performance of ROUTINE2                   | 101  |

| Table 16 | ROUTINES performance statistics              | 103  |

#### CHAPTER I. INTRODUCTION

It was estimated in 1972, that every 5% more facility put into a computer system cost 20% more to achieve, which represented a rapidly rising cost curve [1]. This was mainly due to the need for a more complex operating system.

The complexity of an operating system designed for a multiprocessor system is usually greater than that designed for a single processor system [2]. In the general-purpose multi-arithmetic logical unit configuration, the difficulty is mainly in the implementation of an integrated control within the operating system. For example, synchronization, task splitting, and scheduling are areas where the presence of more than one processing unit increases the supervisor's complexity.

As is well-known, most of the computer system's cost goes to the software design, especially the operating system. A strong, fast-rising relationship between the complexity of the operating system and the total system cost mandates the need for a more efficient utilization of current technology to support the operating system. It is important to notice that a more complex operating system not only means a higher system cost, but also means a larger percentage of the processing power devoted to executing the operating system code. Thus, the existence of powerful, fast, inexpensive microprocessors makes it worthwhile to study the possibility of utilizing current technology to support the execution of some operating system functions. This is especially attractive in the case of a modular, structured, operating system because a high

degree of parallel operating system processing should be achievable.

Extensive studies have shown that a computer system formed by interconnecting many small micro or miniprocessors achieves a better cost/performance ratio and higher reliability than a powerful, large, and complicated single processor system [3, 4, 5]. This concept is appealing, not only at the computer system level, but possibly at the operating system level. If we can look at the operating system by itself as a system, we may think about the possibility of multiprocessing some of its functions, especially those that lend themselves to parallel processing. Multiprocessing of operating system functions using inexpensive VLSI chips is the subject of this dissertation. To prove the point, a submodule for the exact implementation of the least recently used replacement policy in a demand paging system was designed, built, and tested. This work is described in the various chapters of the dissertation as noted below.

Chapter II has been devoted to reviewing some related literature. In Chapter III, an approach for supporting an operating system has been introduced. In Chapter IV, a specific example of a support module for a deadlock avoidance scheme has been described along with its related literature review. Chapter V contains a detailed description of the design of a module to implement the exact least recently used replacement policy. Also in Chapter V, the description of a submodule that was designed, built, and tested is given along with the least recently used routine, hardware circuit, and test circuit details. The data obtained

from testing the submodule along with some remarks and comments are given in Chapter VI. Chapter VII contains the conclusion.

#### CHAPTER II. LITERATURE REVIEW

The amount of literature dealing with the subject of microprocessor based support for an operating system is very limited. However, some publications can be related to this subject in a broad sense. These will be reviewed in this chapter. Since Chapters IV and V will provide specific application examples, it is more appropriate to review their related literature in those chapters.

A study in 1972 provided an example of operating system measurements and indicated the need for better hardware assistance in monitoring and adjusting the operating system performance [6]. Afterwards, multiprocessing systems and their operating systems were subjected to extensive research. It was found that multiprocessing systems achieved a better cost/performance ratio and better reliability than single processor systems [3, 4, 5]. One study used analytical and numerical techniques to compare job turnaround time and throughput rate of three multiprocessor system models with that of a single central processing model of equal processing rate [4]. The results indicated that multiple slow processors may sometimes be used to replace a fast central processor without significant performance degradation. The investigator concluded that this would be increasingly attractive as the cost of microprocessors continued to decrease. An interesting paper published in 1977 discussed different multiprocessor systems and envisioned two main types of control in multiple instruction multiple data (MIMD) architecture [2]. The first was fixed mode, in which one or more processors were dedicated to execute the operating system. When some

other processor terminated its task, or when all other processors were busy and a higher priority task had to be initiated, it was the responsibility of the dedicated processor(s) to schedule, terminate, and/or initiate processes. An advantage of such a scheme is that a special purpose hardware can be embedded in the design, hence decreasing the executive's overhead. The other type of control was the floating control mode. In this mode, each processor could have access to the operating system and could schedule itself. This mode had a reliability advantage over the fixed mode. The investigator concluded that despite the decreasing cost of hardware due to large scale integration, the increased complexity in communication and the overhead in the operating system should be taken seriously when thinking about distributed function systems. The investigator also suggested that the challenging problems in the design of coherent architectures of viable and efficient operating systems, and in the inclusion of evaluating tools both during the design process and in the completed system itself, would restrict for some time the range of useful systems.

Although it has become an established fact for many applications that multiprocessor systems are superior to single processor systems in terms of the cost/performance ratio despite the increased operating system complexity, it is not clear whether a homogeneous architecture is better to adopt. Apparently, homogeneous systems have some advantages in terms of reliability and design simplicity [7], whereas heterogeneous architectures have the merits of flexibility and performance improvement with appropriate load sharing [8].

A very interesting system with strong relationship between hardware architecture and the operating system architecture was described in 1977 [3, 9]. The system was called Poly-Processor System (PPS). The system was developed for time sharing services and consisted of a processor subsystem, a memory subsystem, and a connection subsystem. The processor subsystem consisted of a number of functionally specialized processors, which covered six functional classes. The set of functions for each processor class corresponded to the partitioning of conventional operating system functions. Furthermore, the functions of each processor class were divided into functionally specialized subclasses and each of six processor classes consisted of many subprocessors or modules. The memory subsystem consisted of six memory classes, which were categorized according to the behavior and characteristics of stored information. These classes were introduced to add changeability to the functions of processors, to prevent errors from spreading, and to reduce the memory access conflicts. Since the reliability of the system was affected by rigidly assigning the functions to the processor, a dynamic microprogramming technique was used to move a process from a failed processor to a processor that had at least as much connection as the failed processor.

The most important issue in the design of such a multiprocessor system as the PPS was to devise a connection subsystem between processors and memory modules that would be effective for highly parallel and closely cooperative processing. In order to achieve parallel processing, information, i.e. programs and data used in the system, was divided into

three categories: private information, command data, and shared data. Private information was stored in a memory provided exclusively for each processor. Command data which were used to initiate a program in another processor such as requests, inquiries, and answers, were transferred directly between processors. Shared data were stored in a memory shared by several processors. For command data and shared data, two different connection modules were provided; the interprocessor connection module used a common bus technique, and the processor-memory connection module used a crossbar switch technique.

Extensive studies of the PPS system pointed out the validity of relating the hardware architecture to the operating system structure [3, 9]. However, the system suffered some drawbacks which were noted by the authors who described and studied the system's performance.

These drawbacks can be summarized as follows:

- (1) The system was inflexible since it was hard to modify and expand.

- (2) The system was tailored to fit a time-sharing service giving no potential for applicability in other system environments.

- (3) Reliability was relatively limited by the small number of processors connected to main memory.

- (4) System cost increased largely because of implementing the interprocessor class.

- (5) System performance was degraded by the command data transmission overhead.

However, the PPS-related studies certainly established a good

background in searching for other approaches.

It is appropriate to conclude the literature review by remarking that there should be ways to support and multiprocess operating system functions regardless of the hardware architecture. It should be possible to apply many concepts whether the supported system is a single or multiprocessor system.

Additional literature will be reviewed in Chapters IV and V when specific operating system support examples are to be introduced.

# CHAPTER III. MODULAR MULTI-MICROPROCESSOR BASED SUPPORT FOR AN OPERATING SYSTEM

On the average, 10-30% of a computer system's processing time is spent in executing operating system-related activities [6]. This not only represents an overhead in terms of central processing unit time, but can also be viewed as a load on other system resources such as main memory and shared buses, thus limiting the system performance. It can be said that in some way it is wasteful to execute some operating system functions on a main processor or processors. The data provided on the PPS system performance indicated that, on the average, 12 bytes of command data passed to an operating system module every 250 accesses by another processor [3]. The command data were used to initiate a program in another processor. It consisted of command code codes and parameter words which specified the program execution details. This was the case when only six modules were incorporated. If the number of modules has been increased such that every module became responsible for only one function, one would have expected a transaction size to be less than 12 bytes (no need for command code). Moreover, the interprocessor communication period could have been much longer.

An approach that might provide better cost/performance ratio will now be described. The approach is general enough so that it is applicable to different system architectures. The idea is to use as many support modules for the operating system as needed. Each module contains one or more microprocessors. The operating system may be viewed as composed of two parts: (1) A software part residing in main memory; and

(2) A microprocessor-based modular support part.

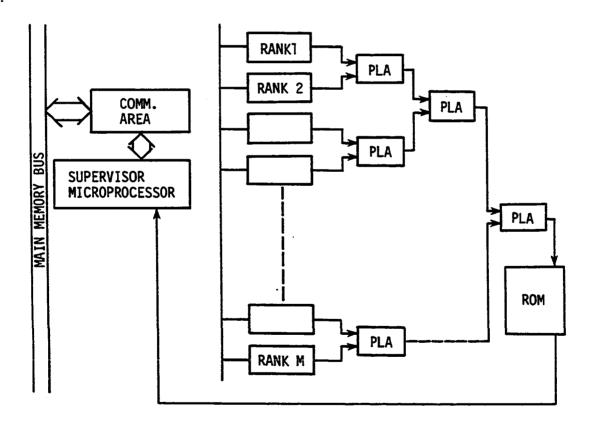

Communication between the two parts is carried out through dedicated, relatively small, reserved areas of main memory space. This is shown in Figure 1. The communication area of a module is also a part of the module's memory space and is accessible by both the main system's processor(s) and the module's microprocessor(s). The rest of the module's memory is private to the module and is only accessible by some or all the microprocessors (if more than one microprocessor is utilized in the module). This kind of architecture makes the idea applicable to a wide spectrum of system architectures. This occurs because common memory accessible by the main system processor(s) almost always exists in tightly coupled multiprocessor systems and certainly in single processor systems. Consider, for example, a single bus homogeneous multiprocessor system supported by a modular heterogeneous multimicroprocessor system as shown in Figure 2. Different aspects regarding the design and performance of such a system can now be pointed out.

#### Support Modules

Each support module consists basically of:

- (1) One or more microprocessors;

- (2) A private memory; and

- and a dedicated bus connected to the microprocessor(s).

The private memory is generally larger than the communication area and can be slower. The former need only match the microprocessor's speed, while the communication memory has to be fast enough to match main

Figure 1. Communication technique between the support system and the main system

Figure 2. A homogeneous main system supported by a heterogeneous modular support system

system's processor(s) speed. Some advantages of such an organization are:

- (1) Memory space, as seen by the main system, is much less than the actual memory space used by the module to process a function.

- (2) Slower, hence cheaper, private memory is used to execute operating system functions. However, the overall system speed may improve because functions will be executed in parallel.

- (3) Module demand on main system resources is minimum, leaving more resources such as central processing unit time, main bus, memory space, etc., for productive work.

Different kinds of microprocessors may be used in different modules. The selection of a certain kind for a module should be dependent on the function to be performed, as well as the characteristics of the microprocessor. The number of micros in a certain module should depend on the frequency the module is invoked, as well as the nature and length of the function. Some modules might have to perform jobs like monitoring functions or performance measurement. Such modules would have to submit a report to the main system which uses the report either to dynamically adjust some operating system parameters, or to help some operating system functions such as the implementation of the exact least recently used replacement policy in a demand paging system. In such cases, the number microprocessors would depend on the arrival or event rate as well as the code execution time of a microprocessor's routine.

#### Reliability

Because of the specialized nature of the modules, it might seem that there is a reliability problem. However, many techniques to improve the reliability of the support system are available; for instance, redundancy within a module, or redundancy at the module level, may be implemented at some insignificant cost. Besides, an extra microprocessor per module can be employed to perform supervisory and status checking functions of the other elements. In case of a microprocessor failure, the supervisor micro may take over its job and inform the main system about the problem. Redundancy at the module's level might also be feasible because of the low cost of microprocessors and of hardware in general.

Another interesting idea that could enhance both reliability and flexibility is to use a pool of microprocessors which are assigned functions dynamically. This idea was implemented in designing a file storage/retrieval system by Trans-A-File Co. [10]. The system used a set of microprogrammed microprocessors to perform a wide variety of tasks that were dynamically allocated to it. The control programs were stored on a tape and transferred upon allocation of a task to a microprocessor's memory. The trade-off in the design was mainly the response time required to reconfigure the system. However, in our case the idea may be utilized in the suggested support system to assign the function of a failed module to a stand-by module.

An idea that can result in a very reliable system is to store all module function codes in secondary memory. In case of module's failure,

its corresponding code is transferred to the main memory and is temporarily executed by the main system processor(s) without support.

#### Cost

With the constant decline in the cost of powerful microprocessors and hardware in general, it is feasible to use the brute-force approach which employs a large number of microprocessors to perform some function. For example, the author designed and built a part of a module (submodule) for implementing the exact least recently used replacement policy in a demand paging memory management system with a hardware cost around \$300. Two MC68000 microprocessors at \$104 each were employed for both testing and implementing the desired function. If a whole module is to be built of eight submodules, only nine microprocessors would be needed and the total cost of hardware should be less than \$3,000. This figure is considered very small compared to the total cost of a multiprogramming computer system, and is nearly negligible.

#### Other Aspects

Some of the operating system functions may not lend themselves to parallel processing or to the idea of support. However, many functions do lend themselves very well to parallel or support processing. These include housekeeping work, scheduling, and monitoring functions. Some examples are sorting and maintaining lists, priority updating, deadlock avoidance-detection schemes, memory replacement algorithms, preparing compaction addresses in segmentation systems as well as finding enough space for incoming segments, job dispatching in multiprocessor systems,

and dynamic bus allocation in multi-bus architectures.

In the next chapter, we will give a specific example of a support module for a deadlock avoidance scheme. In Chapter V, the description of a module for exact implementation of the least recently used algorithm will be discussed, along with the detailed design of a submodule that was actually built and tested.

#### CHAPTER IV. SUPPORT MODULE FOR A DEADLOCK AVOIDANCE SCHEME

#### Introduction

Having introduced a general approach to support an operating system using multi-microprocessor based modules, we are now ready to give the first of two specific examples. The second will be given in the next chapter.

Before introducing our suggested support module for deadlock avoidance schemes, it is appropriate to review briefly some related literature.

One of the operating system functions is to allocate system resources to competing processes. The allocation scheme is usually designed to take care of the possibility of deadlocks. One way a deadlock occurs is when a process holding some resource has to wait for a resource held by another process, while the latter is also waiting for the former to release a resource it holds. Three possible methods to handle deadlocks are available. Each has its own merits and demerits. These methods are:

- (1) Deadlock detection and removal;

- (2) Deadlock prevention, and

- (3) Deadlock avoidance.

Detection algorithms can detect a deadlock that has already occurred and they then try to find a minimum cost way to remove it by deallocating some resources [11, 12]. This approach has the disadvantage of a high time penalty if the resources to be deallocated are non-preemptive.

Moreover, the cost of running a detection and removal algorithm in terms

of overhead is high, especially if the deadlocks occur frequently.

An algorithm is said to have time complexity O(f(n)) if the number of steps it needs to process data of "size" n is cf(n), where f(n) is some function of n and c is a constant [13]. The time complexity of the algorithm provides an approximate indication of the time required to execute it on some computer.

One of the well-known detection algorithms is  $0 \, (\text{mn}^2)$ , where m is the number of resource types and n is the number of tasks [14]. Another algorithm that represents less overhead is  $0 \, (\text{mn})$ , where m and n are as defined above. However, this latter algorithm requires two ordered lists which implies some extra overhead [11, 12].

A more general technique assigns a fixed cost  $c_i$  to the removal (forced preemption) of a resource of type  $r_i$  from a deadlocked task that is being aborted [12]. The algorithm finds a subset of resources that would remove a deadlock at minimum cost.

In general, all detection algorithms insure high supervisor overheads as well as swapping or I/O losses.

Prevention techniques are, in general, designed to exclude the possibility of a deadlock by removing one or more of the conditions necessary for a deadlock to occur. Three different approaches are suggested for the prevention of a deadlock [15, 16]. Nonetheless, each approach has a major disadvantage. The disadvantage of the first approach is poor utilization of system resources by allocating all resources a process needs all at once before it starts execution.

The second approach suffers from the losses due to allowing preemption.

The last approach incurs supervisor overhead and poor utilization of resources.

All avoidance techniques use advance information about process resource requirements. Different models have been developed, each of which is different in the amount of information assumed available.

Two extreme models will shortly be discussed. Intermediate models moderating the drawbacks of the extremes are available. The extreme models are usually simpler, less complicated than others but not necessarily better in terms of overhead. However, simple algorithms may be best suited for microprocessor based support which would take care of the overhead problem, such that main system resource demand could be less than that needed by a fairly complicated algorithm without support. This should be considered an advantage, since simple algorithms with high overhead tend to reduce software complexity, and hence overall system cost. The support hardware would eliminate the overhead penalty. In other words, we don't have to design more complicated algorithms to reduce the overhead; the support system will take care of that.

The first extreme model is the basic model. It assumes the availability of full information (which is impractical). The model consists of a sequence of process steps; during each step the resource usage remains constant. At the beginning of each step, an algorithm is invoked to determine whether the allocation of the requested resources is safe or not. The state of the system at time "t" relates requested and allocated resources. If it is possible to find a valid sequence of the uninitialized process steps such that all processes in the system

can run to completion, the state is safe; otherwise, the state is not safe. This model is clearly impractical and implies high overhead since the algorithm has to run before every process step can execute.

The second model is more practical [14, 17]. It assumes that only the maximum number of resources needed by each process at any time during its execution is known. In particular, each process has a resource vector. Each element in a resource vector represents the maximum number of a certain resource type that will be required by the process at any time during its execution. The algorithm utilizes an unordered list of vectors, each of which represents the rank of a process. The rank of process (i) is defined as the difference between the claim vector c; and the allocation vector a; (a; represents the already allocated resources). The algorithm checks the safety of a request by trying to find a sequence in which a process can run to completion if the request is granted; otherwise, the request is denied. Fortunately, there is no need for backtracking with this algorithm [17]. However, the algorithm is  $0(m^2)$ , where "m" is the number of processes in the system. As "m" gets larger than five, the algorithm's overhead becomes unacceptable.

Another available algorithm is  $0 \text{ (mlg}_2\text{m)}$  [11]. It utilizes a heapsort of the list. However, the algorithm described in [17] will be considered just to prove that even simple algorithms can be supported to execute at a better speed than more sophisticated ones.

#### The Need for Hardware Support

As might have been already noticed, the overhead incurred in deadlock related algorithms is a major concern in designing this part of the operating system. It has been predicted that in future systems sharing an increasing number of individual users, the deadlock problems are likely to acquire greater significance [18]. It has been also predicted that systems which provide a common set of large files (or data bases), available for many users with different access rights, will consider an access to a small subset of records as a resource usage.

Based on the above, it seems appropriate to consider a hardware support module for this important part of the operating system.

#### The Support Module

The support module that will be presented is capable of reducing to a large degree the amount of overhead encountered in traditional deadlock avoidance schemes. The idea can also be extended to work with detection or prevention algorithms. For the sake of an example, Habermann's model for deadlock avoidance will be adopted [14, 17]. In order to understand the function and operation of the module, a brief description of the algorithm follows.

The vector rank; represents the state of process (i) according to the relation

$$rank_i = c_i - a_i$$

where c; is the claim vector of process (i) and a; is its current

allocation. Every element of the vector represents a resource type. A system vector "rem" (for the entire system) represents the remaining number of unallocated resources of all resource types. Upon a request by a process for resource allocation, the algorithm tries to find a sequence in which all processes can run to completion if the request is granted by searching an array that has all process state vectors  $[\operatorname{rank}_i \ i \in 1, 2, \ldots, n]$  as elements. The array is unordered and the search time is  $O(m^2)$ , where m is the number of processes currently holding or requesting resources. It can be proven that backtracking is unnecessary because if an nth process can be found to satisfy the relation

$$rank_i \ge rem + \sum_{i < i} a_j$$

while an (n+1)st process cannot be found to satisfy the (n+1)st relation; the allocation is not safe [17].

The support module employs a number of microprocessors plus some necessary hardware. The number of microprocessors is somewhat arbitrary and can be chosen to fit a desired speed. It is possible to execute Habermann's model as O(km) instead of  $O(m^2)$ , where k is an arbitrary speed factor that also defines the number of microprocessors needed and, consequently, the amount of hardware. It is worth mentioning that the support idea makes it feasible to apply Habermann's model for systems with m > 5 which were supposed to have a prohibitive overhead.

#### 0(km) module, k = 1

This kind of module is feasible only when m is not very large. However, acceptable values of m can be much larger than 5 and m = 30 could be considered reasonable (m is directly related to the degree of multiprogramming). In any case, m is limited by the number of non-preemptive resources.

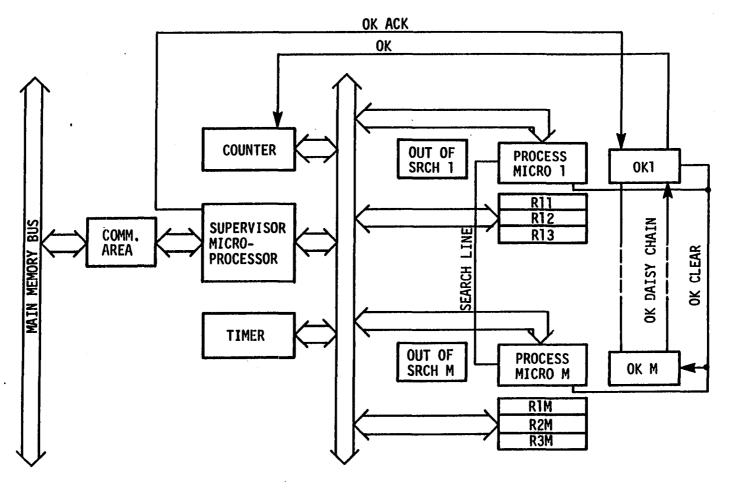

The module contains a total of (m+1) microprocessors of which m microprocessors are to serve the m processes in the system. One microprocessor will serve as the module's supervisor. A microprocessor that represents a process will be called a process micro. It must be mentioned that the number of active processes in the system will vary with time; however, the number of process micros can be selected as the maximum number of active processes allowed by the system at any given time. Another possibility is to select the number statistically, such that the probability that a process gets blocked because there is no process micro available is less than some small value. In such a case, the correspondence between a process and a microprocessor would be variable with time and it is the responsibility of the supervisor to assign processes to microprocessors. Figure 3 shows the organization of the module. A small bus is utilized to connect all the microprocessors within the module, while all communication between the main system and the module is done through a small area of main memory space accessible only by the supervisor.

Associated with process micro (j) are two flags 'ok,' and 'out of SRCH,'. Also, three external registers, R1j, R2j, R3j, are associated

Figure 3. Organization of the O(m) module

with process micro (j) (jɛl, 2, ..., m). Rlj and R2j will be used as communication buffers between the microprocessors within the module; therefore, they should occupy the same locations in all microprocessors' address space. R3j will act as a status and control register. All registers are private to the module's memory space and are not accessible by the main system. The function of the two flags associated with each process micro will be discussed when the operation of the module is to be introduced.

Two modes of operation control the local bus. These modes are parallel write and addressed read/write. Part of the address on the bus defines the mode of the bus cycle. Registers Rlj (jɛl, 2, ..., m) will always be written into simultaneously through a parallel write cycle initiated by the supervisor and, hence, they should only occupy bl bytes of its address space, where bl is the number of bytes in Rl. This also applies to registers R2j (jɛl, 2, ..., m) except that any microprocessors in the module can initiate a parallel write into them. Registers R3j (jɛl, 2, ..., m) are to be addressed separately only by the supervisor, and hence occupy mb3 bytes of its address space, where b3 is the number of bytes in R3. Registers Rlj (jɛl, 2, ..., m) will be used to receive supervisor messages, while registers R2j (jɛl, 2, ..., m) will be used to store the rem vector after each search step. As mentioned before, registers R3j (jɛl, 2, ..., m) are to represent control/status registers for the process micros.

Operation The supervisor microprocessor continuously monitors the communication area looking for a search message from the main system.

When one is found, it starts a search procedure by broadcasting the request and the requesting process number to all Rlj registers. It also calculates a modified rem vector that corresponds to the rem vector if the request is granted. The modified rem vector is broadcasted to all R2 registers using a parallel write mode cycle. Each process micro compares the requesting process number to the number of the process it represents. The one that has a match becomes responsible for starting the first search step by activating the search line. Upon receiving the search signal, all active process micros start searching by comparing their rank vectors with the modified rem vector. If rank; is less than or equal to the rem vector, then process(j) is capable of running to completion if the request is granted, and hence, the process micro(j) sets its associated 'Ok; flag. Note that only micros that have active processes in the system should participate in the search; these will be called active micros. All Ok, (jɛl, 2, ..., m) are daisy chained, such that if any of them is set during a search step, a signal is generated to increment a counter 'COUNT'. The supervisor monitors the counter and whenever it detects an increment, it generates an acknowledge signal 'OKACK' that ripples through the daisy chain and stops at the first set 'Ok,' flag, generating another signal that sets the corresponding 'OUT OF SRCH' flag. This tells process micro(N) that it has been accounted for, and that it should get out of the search after initiating the next search step. Process micro(N) calculates the new modified rem vector, stores it into all R2j (j $\epsilon$ 1, 2, ..., m) registers of active micros. A bit in R3j can

represent the status of processmicro(j) "active" or "inactive". This bit may control the acceptance of parallel write operations in R2;. An out of search process micro is inactive, and it is possible to include the 'OUT OF SRCH' flag in R3. Setting the 'out of SRCH' flag should also set the active/inactive bit to 'inactive' in R3. After broadcasting the new rem vector, process micro(N) clears all 'OK' flags by activating the 'OKCLEAR' line. Finally, it activates the 'SEARCH' line initiating a new search step. The search continues until either all search steps have been completed or an unsuccessful search step is encountered. A successful search means that the number in the counter is equal to the number of active processes, and in such a case, the supervisor has to pass a message to the main system indicating the safety of the request. However, any search step that ends without any 'OK' flag being set means that the result of the search is "not safe," and a message in that effect has to be passed to the main system. For simplicity, it is possible for the supervisor to set the "TIMER" to a certain value corresponding to the number of active processes before initiating the search. The "TIMER" interrupts the supervisor at the end of the expected search period, so that the supervisor can check the counter "COUNT" and determine the safety status of the request.

The support module makes the search time 0(m), since only m search steps are needed at the most. The savings, as compared to Habermann's algorithm, come from the fact that up to m search steps in Habermann's model correspond to one search step in our case. In other words, up to

m search steps are parallel processed in one search step time in the support module.

# 0(km) module, k > 1

The idea and basic operation are the same as the O(m) module discussed above except that each process micro will be responsible for k processes instead of only one. In this case, k 'OK' flags and k 'OUT OF SRCH' flags will be needed per microprocessor. Also, 3k external registers per microprocessor are to be used. However, it is possible to use the same amount of hardware per process micro as the O(m) case giving the microprocessor more work to do internally, on in a private read/write memory such that a process micro can distinguish different process states.

It is clear that a trade-off between speed and the amount of hard-ware is needed. This is because hardware savings are at the expense of execution time. However, this kind of module (k > 1) might be necessitated by a large degree of multiprogramming.

# 0(km) module, k < 1

The idea and module organization are different in this case. It is feasible only when the number of non-preemptive resources in the system is relatively small. The idea is based on the following observations:

- -(!) Limited number of resources means limited number of competing processes.

- (2) The state of the system at any given time is uniquely

determined by the process ranks.

(3) Not all process rank combinations are feasible [17]. Hence, only subset of all system states (determined by process ranks) are to be accounted for.

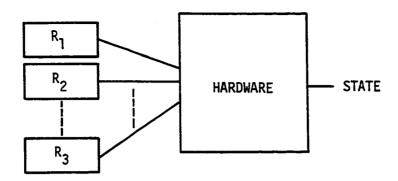

As discussed above, when all process ranks are known, it is possible to run an algorithm to determine the safety condition of the state. Thus, if we consider the ranks as inputs, the state as an output, it is possible to design some hardware to substitute the algorithm as shown in Figure 4.

The hardware is to consist mainly of a Read Only Memory (ROM) and some encoding logic. The ROM stores states corresponding to every feasible rank combination. Only one bit per combination is required. The value stored in a certain bit is determined during the design phase by running the algorithm for the corresponding rank combination.

# Module Organization

Only one microprocessor is needed, as shown in Figure 5. It receives requests from the main system as discussed before. One register per process is used to hold the rank of the process. The combination of all register contents represents the state of the system. Thus, all we need to do is to encode all register contents to produce an address that addresses the ROM. This can be implemented by using a tree of Programmable Logic Arrays (PLAs). Each PLA at the first level combines and encodes two or three registers. At the same time, it suppresses redundant states that are not feasible before presenting its output to the next level. The process is repeated until final address

Figure 4. Hardware substitute for a deadlock avoidance algorithm

Figure 5. 0(km), k < 1 module organization

(representing the state of the system) is presented to the ROM. The output of the ROM (one bit) is the safety state of the allocation request. The microprocessor receives the result and returns a message to the main system. The microprocessor has to return the state of the requesting process to its original state before the request if the request is denied. If the request is safe, the modified process state remains unchanged until the process makes another request or until it releases some or all the resources it holds.

Clearly, the module is very fast compared to the two modules previously described. However, it is only suitable when small numbers of non-preemptive resources are employed in the system.

# CHAPTER V. A MODULE FOR THE EXACT IMPLEMENTATION OF THE LEAST RECENTLY USED REPLACEMENT POLICY

In our second example, we will not only provide the idea of how to implement the exact Least Recently Used (LRU) replacement policy in a demand paging system, but also give the detailed design of a submodule that was designed, built, and tested. The results proved the correctness of the idea and the feasibility of the technique. The next chapter will cover the results of the experiment, while in this chapter all design and implementation details will be given.

#### Introduction

A replacement policy in any memory management system has to find obsolete information in main memory. This is necessary before any new information can be loaded into the Main Memory (MM) if there is no free space available. Free space in MM is created either when information residing in MM is deleted or by purposely swapping out information which is of no immediate interest. If information is deleted, the cleared space can simply be added to the pool of free space. If free space must be created by swapping, we need a criterion by which obsolete information can be distinguished from active information. The right time to look for obsolete information is when memory space is requested while the free space is insufficient. This is why an algorithm which selects the information to be swapped out is called a replacement algorithm. A replacement algorithm applied by a demand paging system allows referencing inaccessible pages and interprets such a reference

as a request to make the page accessible. This is called a "page fault." If handling a page fault is left to the operating system, the operating system must find an obsolete page which can be exchanged for the requested page. The overall objective of a two-level storage management is to have those pages in main memory which have the highest probability of being referenced in the near future. Therefore, nearly all replacement algorithms have as their objective guessing which page in main memory currently has the lowest probability of being referenced. This page is then distinguished as the result of the replacement algorithm.

The simplest replacement policy selects a page at random. This algorithm is implemented by a designer who believes that it is not possible to make an intelligent guess as to which page is least likely to be referenced in the near future. Of course, implementing this policy is trivial, but its performance is poor [17].

Two other straightforward algorithms are the First-In-First-Out (FIFO), and Round Robin (RR). The FIFO replacement algorithm is based on the observation that the probability of referencing a page in the near future is likely to be a decreasing function of the time that the page resides in main memory. It seems, therefore, that the least harm is done if the oldest page is swapped out, that is, the page that was brought into main memory the longest ago. The FIFO replacement algorithm needs the support of a FIFO queue in which pages in the frames are ordered by arrival time. Implementing this algorithm is also trivial.

The Round Robin (RR) algorithm is based on the expectation that the

time intervals during which pages are referenced are reasonably close to an average time length. If this is true, the page with the lowest reference probability is the one in the frame least recently selected. Implementing the RR is very simple by the use of an "own" variable that points to the frame last cleared. When the algorithm is called, it cycles through the frame table starting from where it left off last time until it finds a frame that is in use.

Experiments and measurements have shown that the performance of the FIFO and the RR replacement policies are not good [17].

The Least Recently Used (LRU) algorithm recognizes the fact that some pages are used for longer periods of time than others. For example, a page containing part of a main program or the global data of a program usually has a longer lifetime than a procedure page or page of temporary data. Therefore, the LRU algorithm is based on the assumption that the probability of referencing a particular page is inversely proportional to the time interval between the last reference to the page and the present moment. The page selected by the LRU algorithm is then the least recently referenced page. Numerous studies pointed out the superiority of the LRU algorithm, one of which will now be reviewed.

An interesting study that was done at Princeton University in 1968 provides experimental data on the behavior of programs in a paging environment [19]. The study discussed the problems of paging systems in general and the problem of poor object program behavior in a multiprogramming environment in particular. Specifically, the frequency of page turning (transferring pages in and out of main memory) necessary

for the execution of a program never wholly in main memory, tends to degrade the system performance by introducing an excessive amount of input/output interference. Although the study dealt with different aspects that might affect paging system performance such as page size, number of pages kept in main memory at one time and page replacement algorithms, our concern is with the part that studied the effect of different replacement policies on program behavior. The experiment was designed for the study of programs written for the IBM system/360 model 50 computer and organized to operate under the operating system in use at Princeton University at that time. Each program studied was used as input to an interpreter written for the mentioned machine. The paging behavior of the interpreted program was traced by recording an identification of the new page, determining whether it was a data or an instruction page, and determining the number of instructions executed since the last page request. Simulations were carried out to determine the paging characteristics of the programs when run under different page replacement algorithms. Specifically, the study compared the page fault frequency introduced by the LRU algorithm and by the Belady Optimum Replacement (BOR) algorithm. The BOR is based on a prior knowledge of the entire sequence in which pages are used in the execution of a program [20]. The algorithm is considered the best possible replacement algorithm, but it is totally impractical. Thus, the study selected the BOR as a means of comparing the performance of various practical algorithms with the best possible one.

The study concluded that page turning is a substantial problem in

a demand paging system, and that a least recently used replacement algorithm yields a performance within about 30% of that optimum page replacement sequence. The authors also remarked that with sufficient main memory, the LRU algorithm is an appropriate replacement algorithm in most cases. The authors also mentioned that good agreement had been observed with the study made by Belady under different conditions [19, 20].

Two algorithms that approximate the LRU are the Least Frequently Used (LFU) and the MULTICS [17, 21]. The LFU algorithm counts the number of references to a page and selects the page that had been least frequently used. However, the overhead in the LFU case is very high, since the whole page table has to be searched every time a page fault occurs.

The MULTICS algorithm (also known as the second chance or the clock algorithm) is a much better approximation to the LRU than the LFU. Its overhead is much less and provides better performance than the LFU. However, the MULTICS is still an approximation and incurs an overhead that can be considered high [17, 19].

Despite the near full agreement that the LRU is the best practical replacement algorithm, it was believed that the exact implementation of the LRU is impractical. A common phrase in the literature was that exact implementation of the LRU is not feasible. For instance, in a 1978 book [17], the author said:

An exact implementation of an LRU algorithm is not feasible because of its tremendous overhead on current hardware. It would be necessary to record the time of

reference ever time a page is referenced because the operating system has no way of knowing which reference to a page is the last.

Well, we can say that this is no longer true. A hardware submodule was designed and built to challenge the above statement. The

submodule had the objective of exact implementation of the LRU algorithm,

and proved to be successful at a very low cost. The overhead in terms

of CPU time is possibly less than that of any existing replacement

algorithms.

There are two reasons that made possible the accomplishing of this:

- (1) The availability of low cost, powerful microprocessors and hardware in general, and

- (2) Parallel processing within a support module that works with minimum interference with the main system.

The design and operation of support module will now be given in detail.

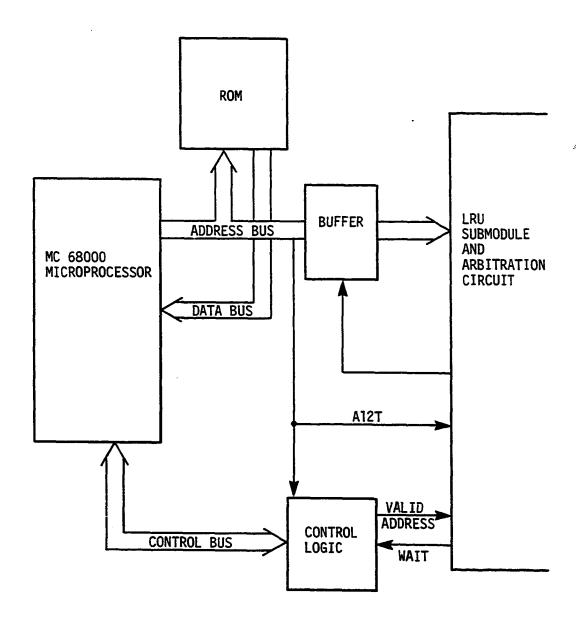

# Exact LRU Support Module Organization

The basic idea in the design is to use a number of submodules that work simultaneously within an LRU module. Each submodule contains a microprocessor and is responsible for finding the least recently used page frame in a certain main memory area. If we divide main memory into 'n' equal areas, then each submodule would be assigned one such area.

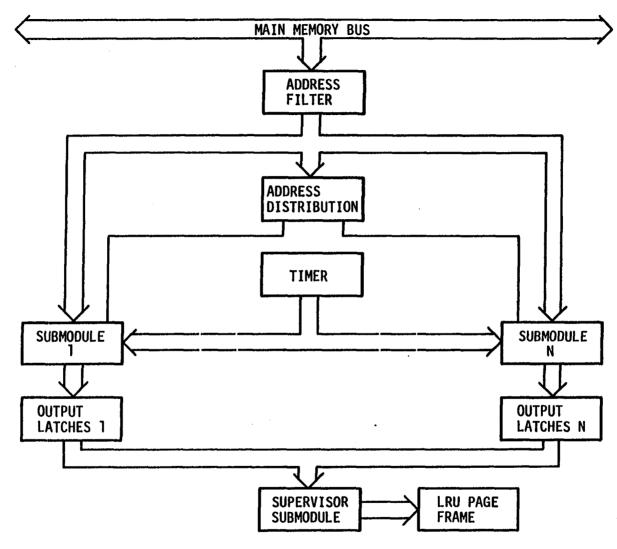

Only the part of the address (on main memory bus) that corresponds to the frame number is the concern of the module. The in-page address is of no importance and can be ignored because we are dealing with pages, not locations. The frame address stream is first filtered out to suppress all consecutive references to the same page except the first one. This means that only the first in a sequence of references to a page is to be considered. It is only necessary to compare the relative reference times to different pages rather than the absolute reference times. This filtering is also important to reduce the arrival rate at the module and to minimize possible interference with the main system as will be explained later. An address distribution circuit, mainly a decoder, is to be used to route the filtered stream to submodules according to the main memory areas they service. A TIMER is incremented every time a filtered frame number is released from the filtering circuit. The TIMER serves all submodules, so only one timer is needed for the whole module. Figure 6 shows the block diagram of the support module. A frame address stream arriving at a submodule will be called an area stream.

A supervisor microprocessor for the whole module is responsible for finding the overall LRU page frame from among the LRU area pages produced by the submodules. The supervisor also has to communicate and present results to the main system. A more detailed discussion about the supervisor's functions will be given later in this chapter.

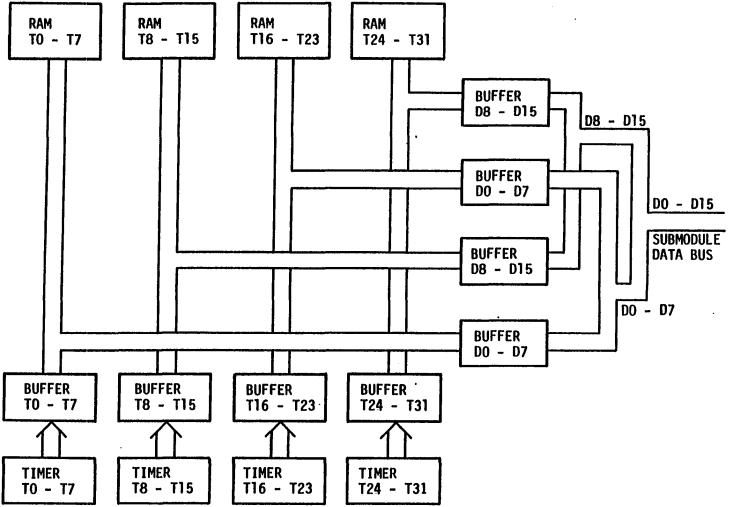

# Submodule Organization

A submodule designed to handle an area stream contains basically a microprocessor, a read/write or Random Access Memory (RAM), and Read Only Memory (ROM). The organization of the submodule is shown in Figure 7. The RAM is used to record the time a page frame is referenced,

Figure 6. Block diagram of the LRU module

Figure 7. LRU submodule organization

while the ROM contains the routine to be executed by the microprocessor. For each page frame in the main memory assigned to the submodule, there is a certain set of locations in the RAM that contains its last time of reference. These locations will be called a Time Record (TR). Every time a frame address arrives at the submodule, the contents of the TIMER are copied into the TR corresponding to the frame address. The frame address itself is used to address the RAM directly to write the TIMER into the frame's TR in RAM.

The microprocessor reads its LRU routine from the ROM without interference from the main system. Three-state buffers are used such that the microprocessor can access its ROM freely at any time without having to interfere with the outside world. The only time interference has to be considered is when the microprocessor wants to access the RAM. An arbitration circuit is used to arbitrate between a time write operation and a microprocessor RAM read cycle.

The submodule is designed to handle 128 main memory page frames. If we assume that the main memory has 1024 page frames, then it can be seen as composed of eight equal areas of 128 frames each. However, the design can easily be modified to assign the submodule different number of frames other than 128. It is much more convenient to divide main memory into a number of areas that is a power of 2, and at the same time assign a submodule a number of frames that is also a power of 2. This could result in a much easier and more efficient design. For instance, a submodule can take care of 64, 128, 256, or 512 frames with different module response times. We chose to assign 128 frames to the

submodule and check the response time. As will be discussed later in the next chapter, the response time obtained with 128 frames/submodule is quite acceptable and doubling the number of frames should result also in an acceptable response time.

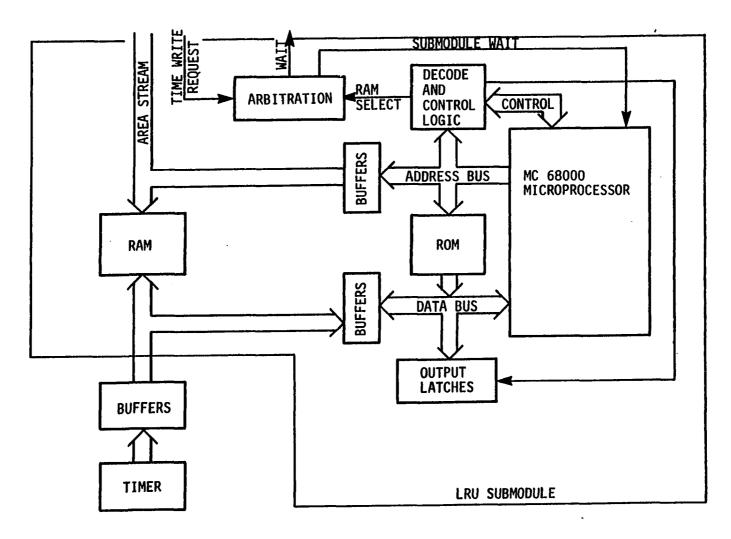

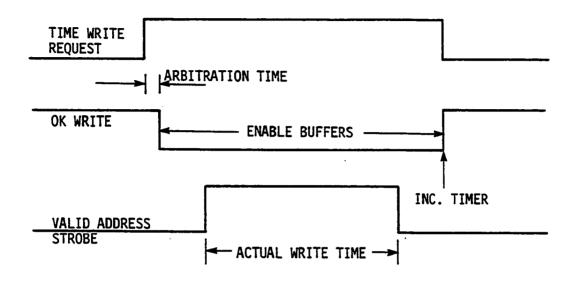

#### Detailed Submodule Design

As shown in Figure 7, both the data and address buses are buffered to control accesses to the RAM. Since the RAM is the source of potential conflicts between the main system (writing a time record) and the submodule's microprocessor (reading a time record), its access is controlled by a simple arbitration circuit. The only case a wait signal is generated by the arbitration circuit and sent to the main system is when the microprocessor is in the process of reading the RAM and a filtered address arrives at the submodule to initiate a time write cycle into the RAM. As discussed later, the probability of this event can be reduced to about 1%. Although our intention was to build and test a submodule, it was also necessary to design and build some extra hardware. For instance, an address generation module capable of producing some prespecified sequences of addresses is necessary to enable testing the submodule. Also, even though only one TIMER circuit is needed for the whole module, it is essential to have a TIMER circuit to test the submodule. In the following section, a detailed description of the major elements in the submodule is given.

# The microprocessor

Motorola's MC68000 [22] was selected as the submodule's microprocessor for the following reasons:

- (1) It is a fast microprocessor that can operate at high clock rate (up to 8 MHZ).

- (2) Its address space is very large; in fact, it is much larger than is needed. This allows the use of some address lines for direct control with virtually no decoding, thus simplifying the design and reducing the cost.

- (3) Most instructions can handle long words (32 bits). This results in a simpler and more efficient routine, especially since the TIMER is chosen to be 32 bits.

- (4) Its data bus is 16 bits wide, which means fewer references to the RAM than would be the case if an 8 bit micro were selected. Thus, fewer potential conflicts with main system are to be expected.

- (5) It is possible to utilize the bus error feature provided by the MC68000 to further reduce the possibility of interference with the main system activities. This will be explained in detail in the next chapter.

Although the MC68000 has many other areas of strength and superiority, only subsets of its capabilities were actually used in the design. For example, it has an advanced interrupt handling scheme that uses seven levels or priority; however, the whole interrupt system had not been utilized in the design. The interrupt system might be useful in

designing the supervisor submodule as a means of interaction with the main system.

#### Arbitration

A simple arbitration circuit is employed to organize and control accesses to the RAM. The arbitration circuit receives requests from the microprocessor to perform RAM read cycles and receives time write requests whenever a valid frame address arrives to the submodule. The request that arrives first is granted the access to the RAM. The arbitration circuit is a simple R-S latch built of fast NAND gates, namely SN74S00 integrated circuits. It must be mentioned that the main system does not actually make requests to access the RAM in the submodule but tries to reference a main memory frame that is assigned to the submodule. The request received by the arbitration circuit is generated within the module and can be interpreted as a request to record the reference time from the TIMER into the frames' TR in the submodule's RAM. Thus, the main system is not actually aware of what is taking place in the support module, but it sometimes may have to wait until the time recording process is completed. Thus, if main memory control logic is employed that is capable of causing a main CPU to wait until the addressed area is free, the resulting wait signal must be logically ORed with the wait signal generated by the support module.

# Random Access Memory (RAM)

The read/write memory or Random Access Memory (RAM) represents a somewhat critical part of submodule design for the following reasons:

- (1) The RAM is the only part of the submodule that can cause access conflicts between the microprocessor (trying to read) and the time recording process (trying to write).

- (2) The addressing space as seen by the microprocessor is different from that seen by the time recording scheme. This will shortly be explained.

- (3) Critical timing problems result because arbitration should be as fast as possible to allow both systems to work at their maximum speed. At the same time, timing specifications of the RAM chips must be met to ensure correct operation. Also, with the existence of two sets of address and data buffers, some other specifications had to be taken into account to enable and disable the buffers at appropriate times.

A set of 6116-4 RAM chips was selected for the read-write memory. They have an access time of 200 ns. Although the 6116 chips are internally organized as 2Kx8 bits, only 128 bytes/chip were actually used. The reason is the unavailability of wider word chips with fewer words.

The RAM is organized as 128 records, each having 32 bits. Hence, four 6116 chips are needed. This is consistent with assigning 128 main memory frames to the submodule.

Since the MC68000 is a 16-bit microprocessor, each Time Record (TR) has to be read from memory in two read cycles. This is not the case when a time write process is to be performed since it is possible to write a whole TR in only one write cycle (the microprocessor is not

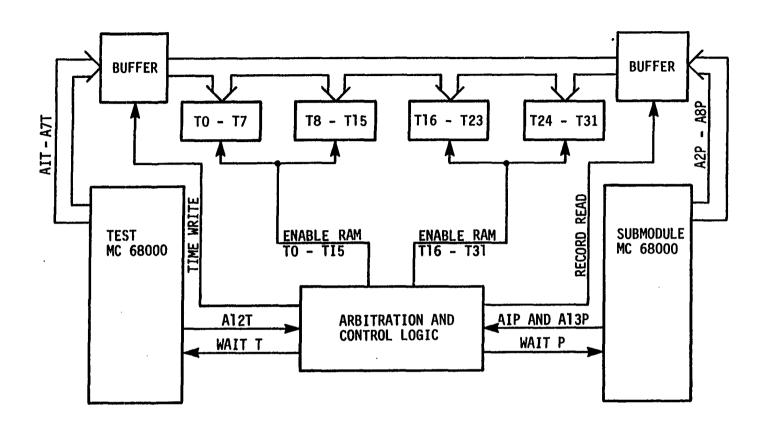

involved here). This has been achieved in the design by using only 7 address lines from the main system, whereas 8 address lines from the MC68000 address have to be utilized to address the RAM. The least significant bit  $(A_1)$  of the MC68000 is used to select either the lower 16 bits  $(A_1 = 0)$  or the higher 16 bits  $(A_1 = 1)$  of a time record. Note that  $A_0$  of the MC68000 doesn't appear on the address bus but is used internally in the case of byte instructions. All the instructions used are either word or long word instructions.

As mentioned earlier, an address stream generation module was built to allow testing the LRU submodule. The former employed another MC68000 microprocessor. To differentiate between the signal lines associated with the submodules MC68000 and those of the test module, we will affix letter P (for processor) to the submodule lines and a T (for test) to the test module lines.

Addressing the four RAM chips is either done using  $A_{2P} - A_{8P}$  of the submodule or  $A_{1T} - A_{7T}$  of the test module. Figure 8 shows the RAM addressing mechanism, as well as major control signals that control RAM operation. The control part is discussed in detail later in this chapter.

To meet the timing requirements, it was found essential to do the arbitration as early as possible in any RAM read or time write cycle. This is achieved by using  $A_{13P}$  as a RAM read request signal for the LRU submodule while  $A_{12T}$  is used as the time write request signal. These signals become valid  $\frac{1}{2}$  clock period in advance of the actual read or write cycle starts since the address lines in the MC68000 are activated

Figure 8. RAM addressing mechanism

$\frac{1}{2}$  clock period before the Address Strobe ( $\overline{AS}$ ) signal is activated. Of course the use of  $A_{12T}$  and  $A_{13P}$  had to be taken into consideration when the programs were designed.

Since the RAM can be accessed from two different sources, a set of 3-state address and data buffers are needed on each side. However, it was essential to include two sets of data buffers (16 bits each) at the LRU submodule side because use of only one 16-bit buffer would short circuit some of the TIMER buffer output lines. This can be understood from Figure 9, which indicates that each TIMER buffer output line goes to one RAM chip and mandates that the same must apply to the other side to avoid short circuits.

The existence of two sets of buffers requires exclusive enabling, that is, one set is enabled at a time. This is taken care of by the arbitration circuit which always has one of its outputs active at a time. If no request is made to access the RAM, both buffers have to be disabled. It must be mentioned that bidirectional buffers are used at the submodule's side to allow the microprocessor to initialize the time records at the beginning of operation.

# Read Only Memory (ROM)

The ROM stores the routine designed to implement the exact LRU algorithm and is considered private to the submodule. This part of the circuit is designed such that the microprocessor can access the ROM at any time freely without any kind of interference from the outside world. This means that a time record can be written into the RAM while the microprocessor is fetching or executing instructions that do not require

Figure 9. RAM data buffering

RAM accesses. Thus, the microprocessor can operate at full speed as long as it is not accessing the RAM while a time record is being written. The existence of data and address buffers permits direct connection of the address and data buses to the ROM. All control signals needed to control the ROM operation are generated directly from the microprocessor's address and control lines.

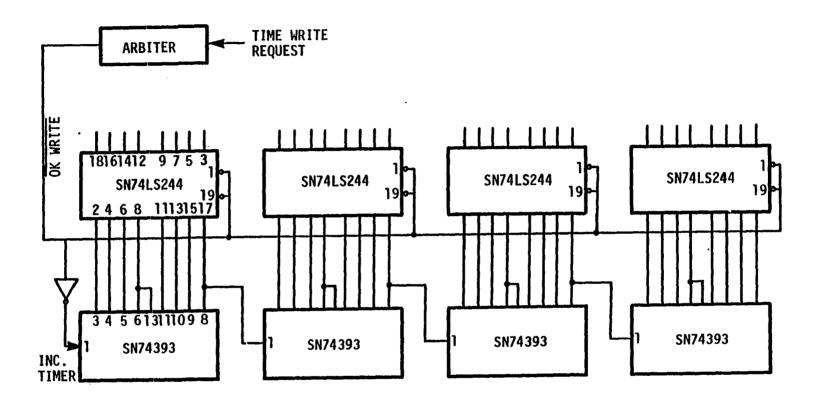

# The TIMER

Although only one TIMER is required to serve all submodules, it was necessary to build one to allow testing the submodule. The TIMER was chosen to be a 32 binary counter that is incremented every time a valid address is released from the filtering circuit. The SN74393 chips are utilized to build the TIMER. Each chip can be configured to form an 8-bit binary counter; therefore, four chips are needed to build the 32-bit counter.

Since the arrival of a valid frame address to the module implies incrementing the TIMER and writing it into the RAM, the stability of all TIMER bits must be ensured during the write operation. This is accomplished by performing the increment operation immediately after the write operation is completed. The rising edge of the signal that enables the TIMER buffers (active low signal) is used to increment the TIMER. However, the TIMER needs a maximum of 240 ns to stabilize all 32 bits, which means that 240 ns must elapse between two consecutive time write operations to ensure correctness. It is possible to solve this problem by utilizing a single shot or monostable multivibrator that has a period of slightly over 240 ns (say 250 ns). The monostable

is driven by the TIMER increment signal and its output is used to inhibit any successive signal that arrives during the 250 ns period.

Although this technique allows two time records to have the same value, it should not be considered a problem for two reasons:

- (1) The probability of switching from one page frame to another after just one reference is very small (locality of reference)

[17].

- (2) If a page is to be selected as the LRU from two pages that have the same reference time, it does not make much difference which one is selected. This is because an output is produced by the module, say every 2-3 ms which makes 250 ns negligible. In fact, the 250 ns can be approximated to zero with an error of 1/800 at most.

It is also possible with faster chips than the SN74393 to avoid the whole stability issue, provided that the main system is not too fast. The SN74393 was good enough for the experiments since the address generator speed was not too fast for the selected chips and two consecutive increment signals were more than 250 ns apart. Thus, there was no need for the monostable in our circuit although it is trivial to employ it. Figure 10 shows the TIMER and its buffers while Figure 11 shows a timing diagram of a time recording and TIMER incrementing cycle. Notice that the buffers in Figure 10 are built of SN74LS244 chips which are unidirectional.

Figure 10. The TIMER and its buffering

Figure 11. Time recording timing diagram

# Decoding and control logic

Low power Schottky TTL chips are used throughout the submodule except for the arbitration circuit. This makes it possible to directly load the MC68000 microprocessor pins with more than one load. Actually, some pins are loaded with up to five loads directly without buffering. Moreover, as is well-known, Schottky logic is superior in handling unwanted noise signals because of the existence of a clamping diode at each input.